10.8 Synchronous and Asynchronous Input

1. Menjelaskan

Synchronous and Asynchronous Inputs.

2. Melakukan simulasi Synchronous and Asynchronous

Inputs.

Gerbang NAND menghendaki semua inputnya bernilai 0 (terhubung dengan ground) atau salah satunya bernilai 1 agar menghasilkan output yang berharga 1.

Spesifikasi:

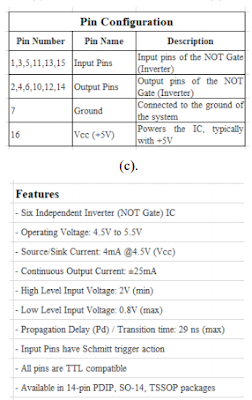

Konfigurasi pin:

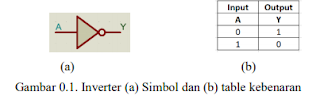

b. Inverter (NOT)

Inverter atau pembalik(NOT) adalah suatu gerbang yang bertujuan untuk menghasilkan logika output kebalikan dari logika input. Adapun simbol dan tabel kebenaran gerbang Inverter seperti berikut:

c. Logic State

Perangkat elektronik yang akan membuat keputusan logis berdasarkan berbagai

kombinasi sinyal inputnya. Mungkin memiliki lebih dari satu input tetapi hanya

memiliki satu keluaran digital.

d. Logic Probe

Logic Probe berfungsi untuk melihat output.

a. Gerbang NAND

Gerbang NAND akan menghasilkan keluaran (Output) Logika 0, apabila semua masukan (Input) pada Logika 1 dan apabila ada sebuah masukan (Input) yang bernilai Logika 0, maka akan menghasilkan keluaran (Output) Logika 1.

Transistor Gerbang NAND

Secara sederhana, gerbang logika NAND 2 input dapat dibangun menggunakan RTL Resistor-transistor Switch yang terhubung bersama degan input yang terhubung langsung ke basis transistor, dimana transistor harus dalam keadaan cut-off "MATI" untuk keluaran Q.

Gerbang logika NAND dapat menghasilkan fungsi logis yang diinginkan dengan simbol berupa gerbang AND standar dengan tambahan lingkaran (biasa juga disebut sebagai "Gelembung Inversi" pada bagian output yang mana mewakili gerbang NOT) yang disebut sebagai operasi logika NAND.

Jenis Gerbang Logika NAND:

Gerbang NAND 4 Input:

Berdasarkan gambar diatas ekspresi Boolean untuk gerbang NAND 4 input yaitu : Q = A.B.C.D

b. Inverter(Gerbang NOT)

Gerbang NOT merupakan gerbang di mana keluarannya akan selalu berlawanan

dengan masukannya. Bila pada masukan diberikan tegangan ,maka transistor

akan jenuh dan keluaran akan bertegangan nol. Sedangkan bila

pada masukannya diberi tegangan tertentu, maka transistor akan cut off,

sehingga keluaran akan bertegangan tidak nol.

Materi:

Kebanyakan

flip-flops memiliki input sinkron dan asinkron.

Input

sinkron adalah mereka yang efeknya pada output flip-flop disinkronkan dengan

input jam. Input R, S, J, K dan D semuanya adalah input sinkron.

Input

asinkron adalah input yang beroperasi secara independen dari input sinkron dan

sinyal clock input. Ini sebenarnya menimpa input karena statusnya menimpa

status semua input sinkron dan juga input jam. Mereka memaksa output flip-flop

untuk pergi ke keadaan yang telah ditentukan terlepas dari status logika dari

input sinkron.

Input

PRESET dan CLEAR adalah contoh input asinkron. Saat aktif, input PRESET dan

CLEAR menempatkan output Q flip-flop masing-masing dalam status '1' dan '0'.

Biasanya, ini adalah input LOW yang aktif. Ketika diinginkan agar fungsi

flip-flop sesuai dengan status input sinkronisnya, input asinkron disimpan

dalam keadaan tidak aktifnya. Selain itu, kedua input asinkron, jika tersedia

pada flip-flop tertentu, tidak diaktifkan secara bersamaan.

• Buka aplikasi proteus

• Pilih komponen yang dibutuhkan, pada rangkaian ini dibutukan komponen logic state, gerbang NAND, NOT, dan logicprobe.

• Rangkai setiap komponen menjadi rangkaian yang diinginkan

• Ubah spesifikasi komponen sesuai kebutuhan

• Jalankan simulasi rangkaian.

Pada rangkaian ini, selagi input asinkron ada yang berlogika 0, maka input sinkron diabaikan, bisa logika 0 maupun 1. Ketika PS berlogika 0, CLR berlogika 1, maka output Q berlogika 1 dan Q berlogika 0. Saat PS berlogika 1, CLR berlogika 0, maka output Q berlogika 0 dan Q berlogika 1.

Kemudian ketika input asinkron semua berlogika 1, maka input sinkron akan berpengaruh. Ketika J dan K berlogika 0, clock merubah dari 1 ke 0 karena aktif rendah, maka Q nya terjadi tanpa perubahan (sama dengan kondisi sebelumnya). Ketika J berlogika 0 dan K berlogika 1, maka Q berlogika 0. Ketika J berlogika 1 dan K berlogika 0, maka Q berlogika 1. Ketika J dan K berlogika 1, output akan berada di posisi terbalik, Q=Q.

Datasheet Gerbang Logika NAND (IC 7410)

Tabel 1 : Present State dan Next State Gambar 1:

Present State | Next State | ||

Q1 | Q0 | Clock = 0 | Clock = 1 |

0 | 0 | 00 | 01 |

0 | 1 | 01 | 10 |

1 | 0 | 10 | 11 |

1 | 1 | 11 | 00 |

solution:

1.

B.OR

Tidak ada komentar:

Posting Komentar